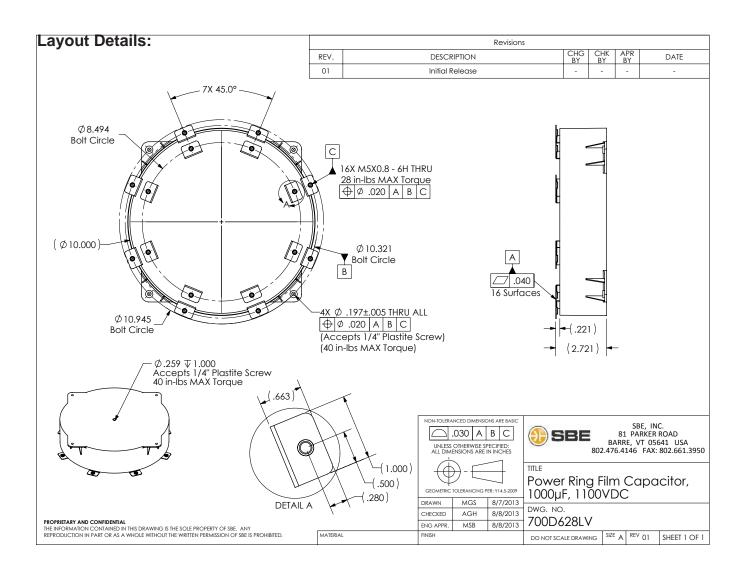

# Power Ring Film Capacitor™ 1000 µF, 1100 Vdc

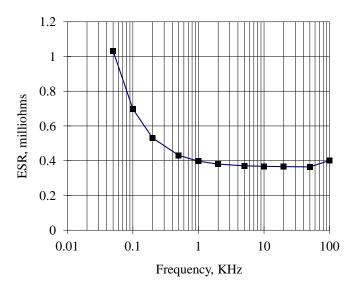

The 700D108911-628 Power Ring is a 1100Vdc, 1000  $\mu$ F DC Link Capacitor with an ESR of 375 micro-Ohms at 20kHz and an ESL of less than 15nH.

| Electrical Specifications |                                                                               | ESL:                                                           | Less than 15 nH in a suitable laminar bus structure |

|---------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------|

| SBE Part #:               | 700D108911-628                                                                | Operating Temperature:                                         | -10°C to +85°C at full                              |

| Capacitance/Tolerance     | : 1000 μF ±10%                                                                |                                                                | DC voltage rating                                   |

| DC Voltage Rating:        | 1100 Vdc                                                                      | Voltage, Temperature<br>De-rating:                             | Contact SBE for applications above 85°C             |

| Dielectric/Construction   | Metallized polypropylene.<br>Single section design                            |                                                                |                                                     |

| Dielectric Withstand:     | Units 100% tested at DC<br>potential of 1300 Volts for<br>two minutes at 25°C | System Fault Current<br>Rating (external to the<br>capacitor): | 10,000 Amps maximum                                 |

#### Typical ESR vs. Frequency:

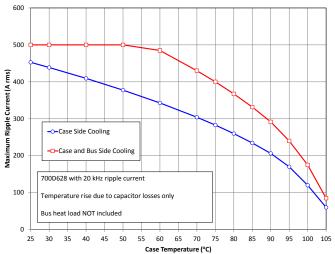

**RMS Current Rating:**

SBE reserves the right to amend design data

## **Thermal Specifications**

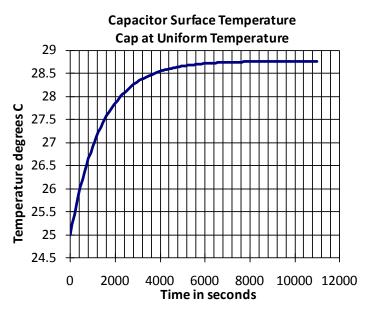

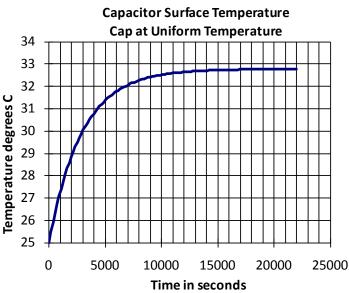

Here are two representations of "Capacitor Surface Temperature over Time" for two specific Thermal Resistances of 1°C/W and 0.5°C/W.

Notes regarding these graphs:

- The thermal resistance is that from capacitor to application. This is a function of the application environment, not the capacitor itself.

- The capacitor can handle extreme current for small duty ratios. Trise occurs very slowly. This is because the capacitor has a high specific heat.

- These charts can be adapted for other currents by multiplying y axis values for any time by (Iapp/254)<sup>2</sup>

- Internal capacitor Trise is added to the capacitor surface/terminal temperature.

- Terminals are assumed to be at case temperature.

## Sample 1.

Capacitor surface temperature rise above application environment @ 207 Amps RMS current load, 10 KHz. Thermal resistance = 0.5°C/W:

### Sample 2.

Capacitor surface temperature rise above application environment @ 207 Amps RMS current load, 10 KHz. Thermal resistance =  $1^{\circ}C/W$ :

telephone: 802.476.4146

fax: 802.661.3950

#### **Mechanical Mounting and Additional Thermal Notes:**

This capacitor is optimized for extremely low self inductance when connected to a suitable laminar bus structure. When so connected, the capacitor is very rigidly attached to such a structure and thus does not necessarily need to be mounted to a chassis. However, the capacitor case can be attached to an application surface/heat sink, etc. if desired. When so mounted, the capacitor can be part of the bus structure support. Use of thermal interface compound between the capacitor case and application surface/heat sink will assist with removal of capacitor and bus heat. Note that the capacitor internal heating is VERY small, and other bus structure heat sources are very likely significantly higher than the heat added to the bus by the capacitor. Capacitor dissipation is approximately 7.5W at 207Arms, from 1-100KHz. It is highly recommended to use infrared thermal imaging from a system cold start to determine the location and relative magnitude of thermal input to the bus. The capacitor may well function as a thermal conduit for bus structure heat, and it will be very possible that the capacitor internal hot spot is less than the terminal temperature. Thermal contour maps are available for some representative conditions.

SBE reserves the right to amend design data

#### Advantages of Power Ring DC Link Capacitors

- Ability to handle higher ripple currents with less capacitance, weight, and volume

- Service life of > 200,000 hours for realistic operating conditions, due to lower losses and better thermal performance

- Minimization of IGBT overshoot and elimination of the need for additional snubber capacitors

- Most effective isolation of DC storage or supply from AC switching artifacts

- Lowest industry ESL at <5nH typical with a properly integrated bus structure

- Smaller inverter packaging

- Overall system cost savings

- Capacitance from 400  $\mu F$  to 2500  $\mu F$  and voltages from 250 Vdc to 1200 Vdc

The SBE Power Ring Film Capacitors<sup>™</sup> utilize traditionally available and economical polypropylene and polyester capacitor dielectric films. However, the *power* of the shape<sup>™</sup> allows for both thermal and electrical performance which has been unachievable in the film capacitor industry to date.

## **Power Ring System Performance**

The combination of lowest available Trise, ESR and ESL coupled with highest ripple current handling capability enable the development of industry leading inverter designs with unbeatable performance and reliability.

### Lowest available Trise for a given ripple current

Lowest available ESL, less than 5nH demonstrated with optimal integrated bus

Lowest available ESR, less than 150 micro-Ohms typical Crown terminal architecture provides for a multitude of current paths which allows the monolithic capacitor to function as a distributed element with a much lower ESR than an equivalent array of smaller parts. SBE has developed a next generation capacitor simulation tool that allows accurate calculation of hotspot temperature to allow optimal rating with excellent reliability.

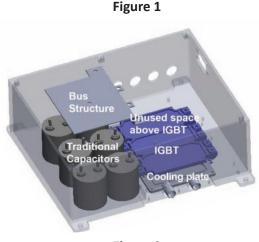

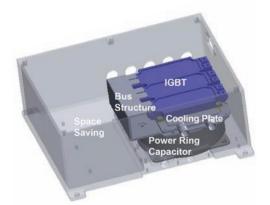

## Integrating the Power Ring in an Existing Design

The "stacked" inverter design evolves from modifying a typical automotive inverter by utilizing the excess space left above the IGBT module (figure 1). By bending the end of the laminar bus plate, the IBGT, die, cooling plate, and the ring capacitor are "stacked" on top of each other in a symmetrical fashion. The ring capacitor is placed underneath the cooling plate. The cooling plate is shared with the IGBT module which is mounted on the top.

Figure 2 shows the "stacked" inverter design after the integration of the ring capacitor and the laminar bus plate. By now combining both aspects of vertical integration and the low temperature rise characteristics of the capacitors, an increase to 50% or more volume reduction is realistically possible. These improvements clearly translate into weight and cost reductions.